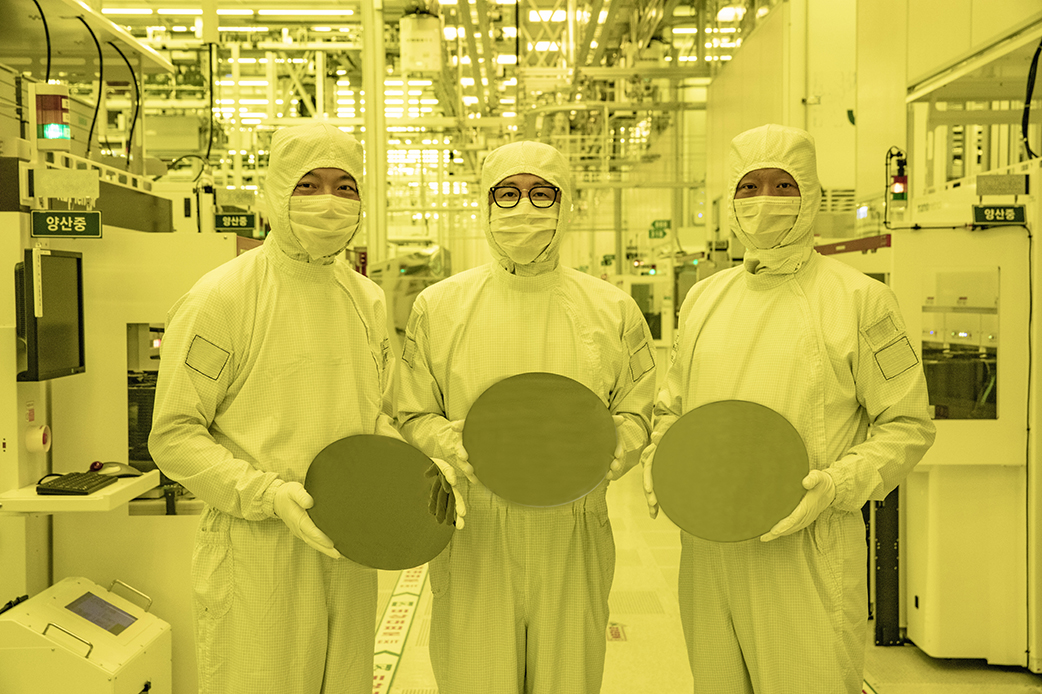

Samsung ha anunciado el inicio de la producción de chips con un proceso de 3 nanómetros (nm) mediante la implementación de la arquitectura de transistores ‘Gate-All-Around’ (GAA), que mejora la eficiencia energética e incrementa el rendimiento.

La tecnología de apilamiento GAA utilizada por Samsung emplea nanoláminas con canales más anchos en lugar de nanocables con canales más estrechos para hacer transistores, una actualización de FinFET, en una superficie que tiene un área 16 por ciento más pequeña que antes.

Esta arquitectura se recoge bajo el nombre de Multi-Bridge-Channel FET (MBCFET), y permite reducir el voltaje de suministro, al mismo tiempo que aumenta la capacidad de corriente de la unidad, superando las ventajas que hasta ahora ofrecería FinFET, según señala Samsung en un comunicado.

El fabricante surcoreano dijo que el proceso se usaría inicialmente para “computación de alto rendimiento y bajo consumo”, con planes para expandir el proceso a procesadores móviles más adelante.

Recomendamos: Samsung presenta innovación para cámaras de smartphones con 200 MP

Samsung afirma que en comparación con el proceso de 5 nm, el proceso de 3 nm de primera generación puede reducir el consumo de energía hasta en un 45 por ciento, mejorar el rendimiento en un 23 por ciento y reducir el área en un 16 por ciento, mientras que el proceso de 3 nm de segunda generación reduce el consumo de energía hasta en un 50 por ciento, mejora el rendimiento en un 30 por ciento y reduce el área en un 35 por ciento.

Los fabricantes han acelerado la carrera por la fabricación de chips más rápidos y eficientes, conforme se acercan a lo que se ha considerado como el fin de la Ley de Moore. Si bien la medida de los nanómetros causa polémica respecto a su verdadero significado e impacto sobre el rendimiento de los microprocesadores modernos, los fabricantes se han aprovechado de esta medida para comunicar una mejora en el rendimiento de estos componentes.

A mediados de 2021, IBM anunció por primera vez la disponibilidad de tecnología de nanoestructura para la fabricación de chips de 2 nanómetros (nm), mientras que un año antes, el fabricante taiwanés TSMC había adelantado que su proceso de 3 nm estaría listo para 2022 y el de 2 nm para 2024.